| 揮憲柦椷宯 | LD | Load |

| LD@ | Load Indirect |

| LI | Load Immediate |

| LSEX | Load with sign extended |

| ST | Store |

| ST@ | Store Indirect |

| RCPY | Register Copy |

| RXCH | Register Exchange |

| XCHRS | Exchange Register and Stack |

| CFR | Copy Flags into Register |

| CRF | Copy Register into Flags |

| PUSH | Push Register onto Stack |

| PUSHF | Push Flags onto Stack |

| PULL | Pull Stack into Register |

| PULLF | Pull Stack into Flags |

| 墘嶼柦椷宯 | ADD | Add |

| RADD | Register Add |

| RADC | Register Add with Carry |

| DECA | Decimal Add |

| SUBB | Substruct with Borrow |

| AND | AND |

| RAND | Register AND |

| OR | OR |

| RXOR | Register XOR |

| CAI | Complement with Add Immediate |

| SHL | Shift Left |

| SHR | Shift Right |

| ROL | Rotate Left |

| ROR | Rotate Right |

| 僕儍儞僾柦椷宯 | JMP | Jump |

| JMP@ | Jump Indirect |

| BOC | Branch On Condition |

| SKNE | Skip if not Equal |

| SKG | Skip if Greater |

| SKAZ | Skip if And is Zero |

| ISZ | Increment and Skip if Zero |

| DSZ | Decrement and Skip if Zero |

| AISZ | Add Immediate and Skip if Zero |

| JSR | Jump to Subroutine |

| JSR@ | Jump to Subroutine Indirect |

| RTS | Return from Subroutine |

| RTI | Return from Intrrupt |

| 偦偺懠 | HALT | Halt |

| SFLG | Set Flag |

| PFLG | Pulse Flag |

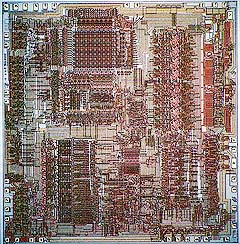

丂塃偼 INS8900偺僠僢僾幨恀丅

丂塃偼 INS8900偺僠僢僾幨恀丅